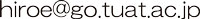

We aim to open up Society 5.0 by media processing technologies. Our research covers a wide range of fields from research to social implementation, including video transmission that connects cyber-physical space with low latency, efficient video transmission using AI, highly compressed video transmission that enables video transmission even in mobile transmission such as 5G, video processing architecture using FPGA, and memory cache systems for video.

・Media Processing Algorithm

In the Media Processing Algorithms research, I study on algorithms for video coding and AI. Specifically, we research for hardware algorithms to improve the performance of VVC which is the latest coding standard and AI-based object recognition at the edge.

・High-performance computing

In High-performance computing, we study parallelization of video processing. Advanced video processing requires enormous amounts of processing using big data in virtual space, and it is an important factor for Scoiety 5.0. We are researching how to utilize the computing power in virtual space.

・Technology for proof of concept

In visualization technology, we are researching techniques to development when mapping video processing to FPGA and low latency implementation methods for interaction in cyber-physical space.

Recent Presentation

-

The 23rd International Conference on Parallel and Distributed Computing, Applications and Technologies(PDCAT'22)

2022年12月7~9日-

"A Partitioned Memory Architecture with Prefetching for Efficient Video Encoders"(Best Paper Award)

Masayuki Sato*1, Yuya Omori*2, Ryusuke Egawa*3*1, Ken Nakamura*2*1, Daisuke Kobayashi*2, Hiroe Iwasaki*4*1, Kazuhito Komatsu*1 and Hiroaki Kobayashi*1

*1 Tohoku University

*2 NTT Device Innovation Center, Nippon Telegraph and Telephone Corporation

*3 Tokyo Denki University

*4 Tokyo University of Agriculture and Technology

-

"A Partitioned Memory Architecture with Prefetching for Efficient Video Encoders"(Best Paper Award)

-

65TH IEEE INTERNATIONAL MIDWEST SYMPOSIUM ON CIRCUITS AND SYSTEMS(MWSCAS 2022)

2022年8月7~10日-

"OpenCL-Based Design of an FPGA Accelerator for H.266/VVC Transform and Quantization"

Hasitha Muthumala Waidyasooriya*1, MAsanori Hariyama*1, Hiroe Iwasaki*1, Daisuke Kobayashi*2, Yuya Omori*2, Ken Nakamura*2, Koyo Nitta*2, Kimikazu Sano*2

*1 Tohoku University

*2 NTT Device Innovation Center, Nippon Telegraph and Telephone Corporation

-

"OpenCL-Based Design of an FPGA Accelerator for H.266/VVC Transform and Quantization"

-

IEEE Symposium on Low-Power and High-Speed Chips and Systems(COOL Chips 25)

2022年4月20~22日-

"An Efficient Reference Image Sharing Method for the Parallel Video Encoding Architecture"

Ken Nakamura*1*2, Yuya Omori*1, Daisuke Kobayashi*1, Koyo Nitta*1, Kimikazu Sano*1, Masayuki Sato*2, Hiroe Iwasaki*2, Hiroaki Koayashi*2

*1 NTT Device Innovation Center, Nippon Telegraph and Telephone Corporation

*2 Tohoku University

- "A Shared Cache Architecture for VVC Coding"(Best Poster Award)

Yoshiaki Kondo*1, Masayuki Sato*1, Ken Nakamura*1*2, Yuya Omori*2, Daisuke Kobayashi*2, Hiroe Iwasaki*1*3, Ryusuke Egawa*4, Kazuhito Komatsu*1 and Hiroaki Kobayashi*1

*1 Tohoku University

*2 NTT Device Innovation Center, Nippon Telegraph and Telephone Corporation

*3 Tokyo University of Agriculture and Technology

*4 Tokyo Denki University

-

"An Efficient Reference Image Sharing Method for the Parallel Video Encoding Architecture"

Recent Journal Papers

-

IEICE Transactions on Information and Systems

- "A Low-Latency 4K HEVC Multi-Channel Encoding System with Content-Aware Bitrate Control for Live Streaming"

Daisuke Kobayashi*1, Ken Nakamura*1, Masaki Kitahara*1, Tatsuya Osawa*1, Yuya Omori*1, Takayuki Onishi*1 and Hiroe Iwasaki*2

*1 NTT Computer and Data Science Laboratories, Nippon Telegraph and Telephone Corporation

*2 Tokyo University of Agriculture and Technology

- "An Efficient Reference Image Sharing Method for the Image-division Parallel Video Encoding Architecture"

Ken Nakamura*1*2, Yuya Omori*1, Daisuke Kobayashi*1, Koyo Nitta*1, Kimikazu Sano*1, Masayuki Sato*2, Hiroe Iwasaki*2, Hiroaki Kobayashi*2

*1 NTT Device Innovation Center, Nippon Telegraph and Telephone Corporation

*2 Tohoku University

- "A Low-Latency 4K HEVC Multi-Channel Encoding System with Content-Aware Bitrate Control for Live Streaming"

Link

Contact

〒184-8588 小金井市中町2-24-16

東京農工大学 小金井キャンパス 10号館503号室

E-mail: