Ion implantation

# Polycrystalline Silicon Thin-Film Transistors Fabricated by Rapid Joule Heating Method

Y. Kaneko, N. Andoh, and T. Sameshima

Abstract—We report n- and p-channel polycrystalline silicon thin film transistors (poly-Si TFTs) fabricated with a rapid joule heating method. Crystallization of 50-nm-thick silicon films and activation of phosphorus and boron atoms were successfully achieved by rapid heat diffusion via 300-nm-thick SiO<sub>2</sub> intermediate layers from joule heating induced by electrical current flowing in chromium strips. The effective carrier mobility and the threshold voltage were 570 cm<sup>2</sup>/Vs and 1.8 V for n-channel TFTs, and 270 cm<sup>2</sup>/Vs and -2.8 V for p-channel TFTs, respectively.

*Index Terms*—Crystallization, defect, joule heating, mobility, polycrystalline silicon (poly-Si), thin film transistors (TFTs), threshold voltage.

## I. INTRODUCTION

**R** APID thermal annealing is useful for fabrication of polycrystalline silicon thin film transistors (poly-Si TFTs) at low processing temperatures and their application to electrical devices [1]–[7]. Laser crystallization has been widely used for rapid formation of polycrystalline silicon films. Poly-Si TFTs with high carrier mobility have been achieved. However, complicated optical equipment is required in order to deliver the laser beam to samples and to control the distribution of laser beam intensity for laser crystallization. We have recently demonstrated a simple crystallization method using electrical-current-induced joule heating [8], [9] Microsecond order rapid heating is achieved by joule heating caused by electrical current flowing thin metal films.

In this letter, we report fabrication of n- and p-channel poly-Si TFTs. Crystallization of silicon as well as activation of dopant atoms are achieved using the rapid joule heating method. The high carrier mobility demonstrates that t he polycrystalline silicon films fabricated by the joule-heating method have a possibility of device application.

#### II. EXPERIMENTAL

Fig. 1 shows the fabrication steps of Poly-Si TFTs. Fiftynanometer-thick undoped amorphous silicon films were formed on glass substrates. Two hundred-nanometer-thick SiO<sub>x</sub> islands with lengths of 25 and 100  $\mu$ m and a width of 70  $\mu$ m were formed on channel regions of the silicon films as the dopant stopper. Phosphorus and boron atoms were implanted at 10 KeV with a density of  $1.3 \times 10^{15}$  cm<sup>-2</sup>, respectively. After removing the dopant-stopping-SiO<sub>2</sub> islands,

The authors are with the Tokyo University of Agriculture and Technology, Koganei, Tokyo 184-8588, Japan.

Digital Object Identifier 10.1109/LED.2003.816580

SiO<sub>x</sub>  $\square$   $\square$   $\square$ a-Si glass Joule heating siO<sub>2</sub> doped a-Si undoped a-Si undoped poly-Si SiO<sub>x</sub>  $\square$ H<sub>2</sub>O vapor Al  $\square$ SiO<sub>x</sub>  $\square$ SiD<sub>x</sub> SiD<sub>x</sub>

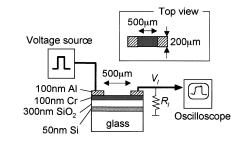

Fig. 2. Schematic apparatus of the rapid joule heating and the cross section of the layered structure of samples.  $5-\mu$ s-pulsed voltage was applied to 100-nm-thick Cr strip with a length of 500  $\mu$ m and a width of 200  $\mu$ m.

crystallization and dopant activation were simultaneously carried out with the joule heating method as shown in Fig. 2. Three hundred-nanometer-thick SiO<sub>2</sub> films were formed on the silicon films. 100-nm-thick chromium films were subsequently formed on the SiO<sub>2</sub> films. Chromium strips with a width of 200  $\mu$ m and a length of 500  $\mu$ m were defined above the channel regions. The resistance of the chromium strips was 65  $\Omega$ . Aluminum electrodes were formed at the edges of the chromium strips to apply electrical voltages. 5- $\mu$ s-pulsed voltages were applied to the samples, as shown in Fig. 2. The electrical current was measured as a voltage at a load resistance connected between the sample and ground using a digital oscilloscope in order to obtain the joule heating energy density per unit area. The joule heat generated at the chromium films

Manuscript received June 4, 2003. The review of this letter was arranged by Editor T.-J. King.

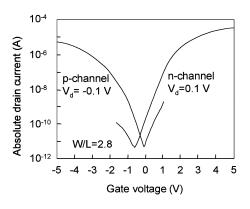

Fig. 3. Transfer characteristics of n- and p-channel poly-Si TFTs with a channel length of 25  $\mu$ m and a channel width of 70  $\mu$ m fabricated at joule heating energy densities at 0.75 and 0.74 J/cm<sup>2</sup>, respectively.

diffuses into the underlying layer and the silicon film are heated by heat flow through the intermediate  $SiO_2$  layer. The silicon channel regions and source drain regions below the chromium strips were successfully crystallized with no substrate heating. Raman scattering spectra and TEM observation revealed that silicon films were crystallized at a joule heating energy density above  $0.58 \text{ J/cm}^2$ , the crystallization threshold, caused by 115-V voltage pulse application [8]. The average grain size was about 100 nm at a joule heating energy density of  $0.74 \text{ J/cm}^2$ . The dopant atoms in the source and drain regions below the chromium strips were also activated. The electrical conductivity became 320 S/cm for phosphorus doping and 280 S/cm for boron doping for joule heating energy density above 0.65  $J/cm^2$ . After removing the SiO<sub>2</sub> layers and the Cr strips, 13.56 MHz-remote-type-oxygen plasma at 100 W, 130 Pa and 250 °C for 30 min was applied to defect reduction in poly Si films [10], [11]. Silicon islands were then defined.  $SiO_x$  films 130–150-nm-thick were then formed as the gate insulator by thermal evaporation of SiO powders in the oxygen radical atmosphere at room temperature [12]. Contact holes were opened and then Al gate, source and drain electrodes were formed. After fabrication of the TFT structure, TFTs were heated at 200 °C with  $1.3 \times 10^6$  Pa – H<sub>2</sub>O vapor for 3 h for improvement of SiO<sub>x</sub> properties [13]–[16]. Measurements of capacitance response with the gate voltage with a frequency of 1 MHz for Al gate metal-oxide-semiconductor (MOS) capacitors with the SiO<sub>x</sub> layer determined that the specific dielectric constant of the SiO<sub>x</sub> layer, the densities of interface traps and fixed oxide charges were  $4.9, 2.0 \times 10^{10} \text{ cm}^{-2} \text{eV}^{-1}$ , and  $3.4 \times 10^{10}$  cm<sup>-2</sup> after the H<sub>2</sub>O vapor heat the treatment, respectively.

#### **III. RESULTS AND DISCUSSION**

Fig. 3 shows the transfer characteristics of the n- and pchannel poly-Si TFTs with a channel length of 25  $\mu$ m and a channel width of 70  $\mu$ m fabricated at joule heating energy densities at 0.75 and 0.74 J/cm<sup>2</sup>, respectively. Sharp increase in the drain current with low gate voltage application was observed for the both TFTs. Fig. 4 shows the effective carrier mobility (a) and the threshold voltage (b) obtained by linear relation of the drain current with the gate voltage for TFTs fabricated at the joule heating energy density from 0.60 to 0.78 J/cm<sup>2</sup>. The effective

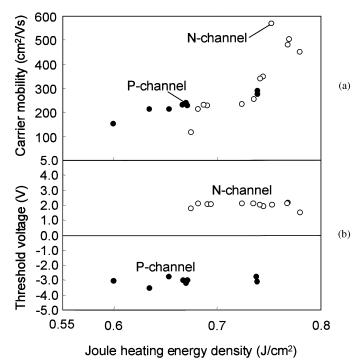

Fig. 4. Effective carrier mobility (a) and the threshold voltage (b) as functions of the joule heating energy density. Open circles represent the carrier mobility and carrier density for n-channel TFTs and solid circles represent them for p-channel TFTs.

carrier mobility increased from 115 to  $570 \text{ cm}^2/\text{Vs}$  as the joule heating energy density increased from 0.67 to 0.75  $J/cm^2$  for n-channel TFTs. It increased from 147 to  $270 \text{ cm}^2/\text{Vs}$  as the joule heating energy density increased from 0.60 to 0.74 J/cm<sup>2</sup> for p-channel TFTs. The high carrier mobility means that silicon films had the high crystalline volume ratio. Moreover there is a possibility of mobility enhancement especially in hole mobility caused by tensile stress [16]. Our previous study revealed that the silicon films crystallized by the present joule heating method had a high tensile stress in the silicon films  $\sim 6 \times 10^8$  Pa due to difference in thermal expansion coefficient between silicon and glass substrate [9]. The threshold voltage distributed between 1.8 and 2.2 V for n-channel TFTs, and it distributed between -3.5 and -2.8 V for p-channel TFTs as shown in Fig. 4(b). Almost same characteristics on the carrier mobility and threshold voltage were obtained for TFTs with the channel length of 100  $\mu$ m.

In order to estimate the density of defect states in polycrystalline silicon films, transfer characteristics shown in Fig. 3 were analyzed using a numerical calculation program constructed with the finite-element method combined with statistical thermodynamical conditions with localized defect states at SiO<sub>2</sub>/Si interfaces and silicon films [17], [18]. The total density of defect states including acceptor and donor type defects trapping electrons and holes, respectively, was estimated as  $1.3 \times 10^{12}$  cm<sup>-2</sup>.

The results of Figs. 3 and 4 demonstrated that the present rapid joule heating can be applied to crystallization of silicon films and activation of dopant atoms in TFT fabrication steps. Fabrication of TFTs with a high carrier mobility and a low threshold voltage is possible at low processing temperature. However, defects remained in polycrystalline silicon probably caused high leakage currents due to carrier recombination at the junctions of channel/doped regions. The density of defect states should be further reduced.

### IV. SUMMARY

The rapid joule heating method using  $65-\Omega$ -chromium strips was applied for crystallization of 50-nm-thick silicon films and activation of dopant atoms for fabrication of polycrystalline silicon thin film transistors (poly-Si TFTs). The joule heating at  $0.6 \sim 0.78 \text{ J/cm}^2$  successfully formed undoped crystalline silicon channel regions and doped source and drain regions. Activation of dopant atoms was also achieved. Defect reduction treatment of 13.56 MHz-oxygen plasma at 100 W, 130 Pa at 250 °C for 30 min was used after crystallization of silicon films. Heat treatment at 200 °C with  $1.3 \times 10^6$  – Pa – H<sub>2</sub>O vapor for 3 h were also applied after TFT fabrication in order to improve electrical properties of SiOx gate insulator. N-channel TFTs had an effective carrier mobility of  $570 \text{ cm}^2/\text{Vs}$  and a low threshold voltage of 1.8 V at a joule heating energy density of  $0.75 \text{ J/cm}^2$ . P-channel TFTs had an effective carrier mobility of  $270 \,\mathrm{cm^2/Vs}$ and a low threshold voltage of -2.8 V at 0.74 J/cm<sup>2</sup>. Those results show that the polycrystalline silicon films formed by the present joule heating have a good enough quality to TFT operation.

#### ACKNOWLEDGMENT

The authors thank Dr. Y. Andoh for his support.

#### REFERENCES

- T. Sameshima, S. Usui, and M. Sekiya, "XeCl excimer laser annealing used in the fabrication of poly-Si TFTs," *IEEE Electron Device Lett.*, vol. EDL-7, pp. 276–278, 1986.

- [2] K. Sera, F. Okumura, H. Uchida, S. Itoh, S. Kaneko, and K. Hotta, "High-performance TFT's fabricated by XeCl excimer laser annealing of hydrogenated amorphous-silicon film," *IEEE Trans. Electron Devices*, vol. 36, pp. 2868–2872, 1989.

- [3] T. Serikawa, S. Shirai, A. Okamoto, and S. Suyama, "Low-temperature fabrication of high-mobility poly-Si TFT's for large-area LCDs," *IEEE Trans. Electron Devices*, vol. 36, pp. 1929–1933, 1989.

- [4] A. Kohno, T. Sameshima, N. Sano, M. Sekiya, and M. Hara, "High performance poly-Si TFT's fabricated using pulsed laser annealing and remote plasma CVD with low temperature processing," *IEEE Trans. Electron Device*, vol. 42, pp. 251–257, 1995.

- [5] S. Inoue, K. Sadao, M. Matsuo, T. Hashizume, H. Ishiguro, T. Nakazawa, and H. Oshima, "Low temperature CMOS self-aligned poly-Si TFT and circuit scheme utilizing new ion doping and masking technique," in *Proc. Int. Electron Device Meet.*, 1991, pp. 555–558.

- [6] S. Uchikoga and N. Ibaraki, "Low temperature poly-Si TFT-LCD by excimer laser anneal," *Thin Solid Films*, vol. 383, no. 19, 2001.

- [7] S. Inoue, K. Sadao, T. Ozawa, Y. Kobashi, H. Kwai, T. Kitagawa, and T. Shimoda, "Low temperature poly-Si TFT-electrophoretic displays (TFT-EPD's) with four level gray scale," in *Proc. Int. Electron Device Meet.*, 2000, pp. 197–200.

- [8] T. Sameshima, Y. Kaneko, and N. Andoh, "Rapid crystallization of silicon films using joule heating of metal films," *Appl. Phys.*, vol. A73, pp. 419–423, 2001.

- [9] —, "Rapid joule heating of metal films used to crystallize silicon films," *Appl. Phys.*, vol. A74, pp. 719–723, 2002.

- [10] Y. Tsunoda, T. Sameshima, and S. Higashi, "Improvement of electrical properties of pulsed laser crystallized silicon films by oxygen plasma treatment," *Japan. J. Appl. Phys*, vol. 39, pp. 1656–1659, 2000.

- [11] S. Higashi, D. Abe, Y. Hiroshima, K. Miyashita, T. Kawamura, S. Inoue, and T. Shimoda, "Development of high-performance polycrystalline silicon Thin-Film Transistors (TFT's) using defect control process technologies," *IEEE Electron Device Lett.*, vol. 23, pp. 407–409, 2002.

- [12] T. Sameshima, A. Kohno, M. Sekiya, M. Hara, and N. Sano, "SiO<sub>2</sub> formation by thermal evaporation of SiO in oxygen atmosphere used to fabrication of high performance polycrystalline silicon thin film transistors," *Appl. Phys. Lett.*, vol. 64, pp. 1018–1020, 1994.

- [13] T. Sameshima and M. Satoh, "Improvement of SiO<sub>2</sub> properties by heating treatment in high pressure H<sub>2</sub>O vapor," *Japan. J. Appl. Phys.*, vol. 36, pp. L687–L689, 1997.

- [14] K. Sakamoto and T. Samaehima, "Passivation of SiO<sub>2</sub>/Si interfaces using high-pressure-H<sub>2</sub>O-vapor heating," *Japan. J. Appl. Phys*, vol. 39, pp. 2492–2496, 2000.

- [15] H. Watakabe and T. Sameshima, "High pressure H2O vapor heat treatment used to fabricate poly-Si thin film transistors," *Japan. J Appl. Phys.*, vol. 41, pp. L974–L977, 2002.

- [16] T. Mizuno, S. Takagi, N. Sugiyama, H. Satake, A. Kurobe, and A. Toriumi, "Electron and hole mobility enhancement in strained-Si MOSFET's on SiGe-on-insulator substrates fabricated by SIMOX technology," *IEEE Electron Device Lett.*, vol. 21, pp. 230–232, 2000.

- [17] H. Watakabe and T. Sameshima, "Polycrystalline silicon thin film transistors fabricated by defect reduction methods," *IEEE Trans. Electron Devices*, vol. 49, pp. 2217–2221, 2002.

- [18] M. Kimura, R. Nozawa, S. Inoue, T. Shimoda, B. O. Lui, S. W. Tam, and P. Migliorato, "Extraction of trap states at the oxide-silicon interface and GRAIN boundary for polycrystalline silicon thin-film transistors," *Japan. J. Appl. Phys.*, vol. 40, pp. 5227–5236, 2001.